2025年12月22日,一则振奋全球科技界的消息传来:美国多所顶尖高校与本土晶圆厂携手,成功研制出一款全新的单片三维(3D)芯片。这款创新性芯片将存储与计算单元在垂直方向紧密堆叠,不仅大幅提升了数据传输效率,更被视为打破束缚人工智能发展“内存墙”的关键突破,为

人工智能硬件的迭代升级注入了强劲动力。

此次研发成果由斯坦福大学、卡内基梅隆大学、宾夕法尼亚大学、麻省理工学院联合美国本土代工厂SkyWater Technology共同完成,是首款在美国商业晶圆厂制造的单片3D芯片。其核心亮点在于垂直互联布线密度创下当前3D芯片的最高纪录,实测与仿真数据显示,该芯片性能较传统二维芯片提升约一个数量级,为人工智能的高效运行提供了坚实的硬件支撑。

传统二维芯片采用“平铺式”设计,所有电路集中在同一平面,数据在存储单元与计算单元之间传输路径较长。而人工智能技术的快速发展,对芯片的数据处理速度和内存容量提出了越来越高的要求,这也让“内存墙”问题愈发凸显。所谓“内存墙”,是指计算单元运算能力持续提升,但芯片内外存储的数据传输速率难以同步跟进,导致处理器频繁“等待数据”,大量算力被浪费,严重制约了人工智能模型的训练效率和运行速度。数十年来,半导体产业通过缩小晶体管尺寸、增加平面器件数量来缓解这一问题,但该路线已逼近物理极限,形成了“微缩墙”困境。

新型单片3D芯片的出现,为破解人工智能发展的双重瓶颈提供了新思路。它采用多层极薄电路层垂直堆叠设计,通过高密度垂直连线实现各层紧密相连,让数据在芯片内部“上下穿梭”,显著缩短了传输路径。这一架构不仅使本地可用内存大幅增加,减少了数据在远端存储与计算核心之间的往返频率,从根本上缓解了“内存墙”问题,更通过垂直方向整合存储与逻辑电路,如同在芯片内部修建了成排“电梯井道”,让海量数据能在不同“楼层”间高速流动,成功突破了“微缩墙”的物理限制。

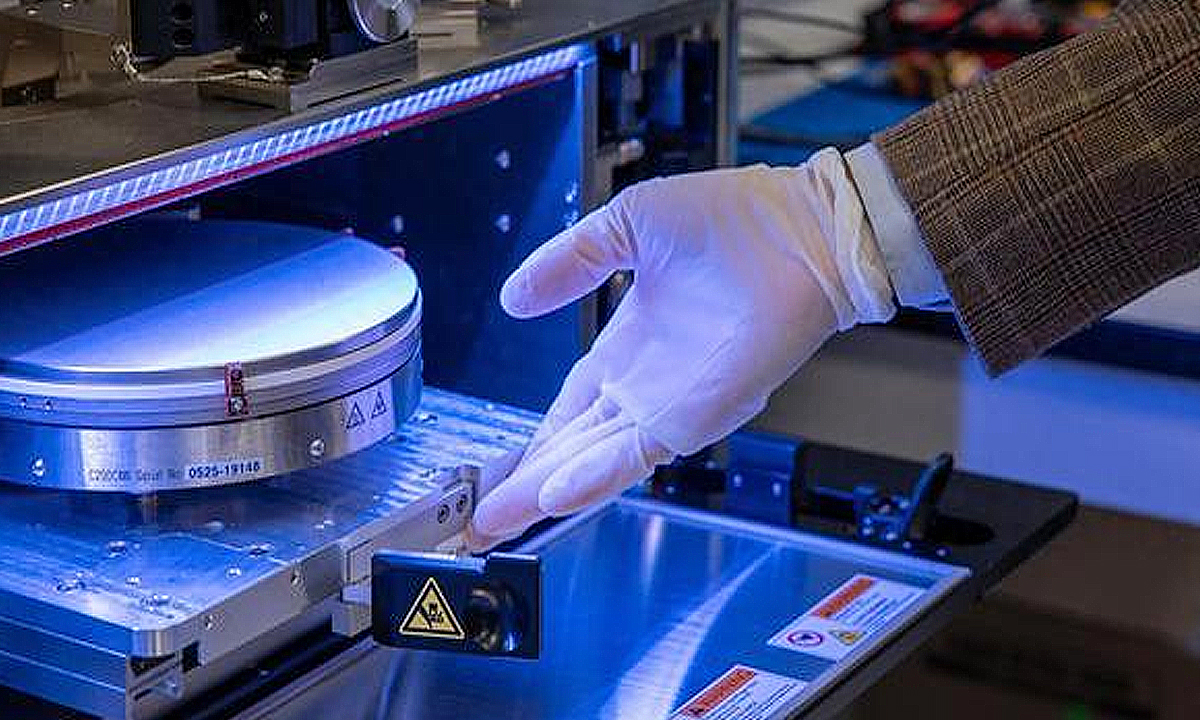

与此前业界尝试的“堆叠芯片”方式不同,这款新型芯片采用“单片”3D工艺,各功能层在同一晶圆上依次直接生长和加工,并通过低温制程避免损伤下层电路,实现了更小尺度上的高密度互联。这一工艺已在SkyWater位于明尼苏达州布卢明顿的商业晶圆厂完成,标志着该技术从实验室概念正式迈向可规模量产阶段,为人工智能硬件的规模化升级奠定了基础。

性能测试数据令人瞩目:早期硬件测试显示,该原型芯片相较传统二维设计性能提升约四倍;进一步仿真结果表明,若继续增加垂直堆叠层数,在包括基于Meta开源大模型LLaMA的实际人工智能负载中,整体性能最高可实现十二倍提升。更值得关注的是,新架构在衡量速度与能效综合表现的关键指标——能源-延迟乘积(EDP)上,理论上有望实现100到1000倍的改善。这意味着该芯片能同时兼顾更高吞吐量和更低单次操作能耗,无需在性能和功耗之间做传统“二选一”,为支撑下一代大规模人工智能系统、实现“千倍硬件性能提升”目标提供了关键路径。

此次突破的意义远超技术本身。在产业层面,它为构建“在美国设计、在美国制造”的先进芯片体系提供了现实范本,有助于提升美国在人工智能硬件领域的创新节奏、供应链安全和技术发展主导权;在人才培养层面,依托美国“微电子公地”计划、加州-太平洋西北AI硬件枢纽等项目的支持,相关高校已围绕3D集成和人工智能专用硬件展开系统化培养,为人工智能硬件产业储备新一代专业人才。

据悉,该项目获得了美国国防高级研究计划局(DARPA)、美国国家科学基金会研究生奖学金项目、三星等多方资助,凝聚了高校与产业界的协同创新力量。随着这款新型单片3D芯片技术的不断成熟和规模化应用,人工智能领域有望摆脱“内存墙”与“微缩墙”的双重束缚,在训练和运行更大、更复杂、更实时的人工智能模型上实现新突破,为全球人工智能产业的发展开辟全新篇章。